Nel post precedente ho brevemente accennato ad un componente di questo particolare modello di nome “PLL”. Come ho scritto è un componente di cui so poco, così come so poco dell’intera sezione di generazione dei segnali video. Ho quindi deciso di approfondire un po’ l’argomento, sia per imparare qualcosa di nuovo (per me) che per “estrarre” dei dati che possono tornare utili a chi si potrebbe trovare a dover riparare questa parte del circuito (o magari a me stesso in futuro).

Da quanto ho letto sono molteplici gli usi di questo particolare circuito in elettronica ma, nel nostro caso, ritengo che sia usato come sintetizzatore di frequenza per ricavare la frequenza necessaria alla (sotto)portante necessaria a gestire i colori del sistema PAL.

Come sappiamo la TV è nata originalmente in bianco e nero. Ricordo bene, quando ero molto piccolo, che in casa avevamo una televisione con soli 3 pulsanti per selezionare il canale (niente telecomando BTW) e che visualizzava solo immagini in bianco e nero. Questo accadeva circa 30 e passa anni fa. Quando, attorno agli anni ’70, si è presentata la necessità di trasmettere immagini per “la nuova figata” che erano appunto le TV a colori dell’epoca si è cercato un modo per farlo che fosse compatibile con le televisioni in bianco e nero che all’epoca esistevano già un po’ ovunque nelle case. In altre parole, si doveva cercare un modo per poter non solo trasmettere le informazioni in più, ma lo si doveva fare in modo che la maggioranza delle televisioni in bianco e nero continuasse a funzionare come se quell’informazione in più non esistesse. Le soluzioni proposte furono varie (di cui una anche della RAI italiana, si chiamava ISA, che però, come una buona fetta del risultato della genialità di pochi italiani, finì in un cassetto per non uscirne più) ma quelle che ebbero maggiore diffusione furono il sistema PAL per l’Europa, Sud America, Cina, Australia, diversi paesi dell’Africa (e in generale quei paesi con le linee elettriche a 50Hz), l’NTSC per il Nord America e il giappone e il SECAM per Francia, Russia e alcuni paesi dell’Africa. Come ho detto conosco poco l’elettronica dei televisori ma se non erro ognuno di questi standard prevedeva, per la trasmissione dei dati sul colore, l’esistenza di una sotto-portante che veniva appunto ignorata da gran parte delle televisioni in bianco e nero sul mercato. In particolare, per il sistema PAL (quello nostro europeo), la sotto-portante contenente i dati dei colori ha una frequenza di 4.433618 MHz.

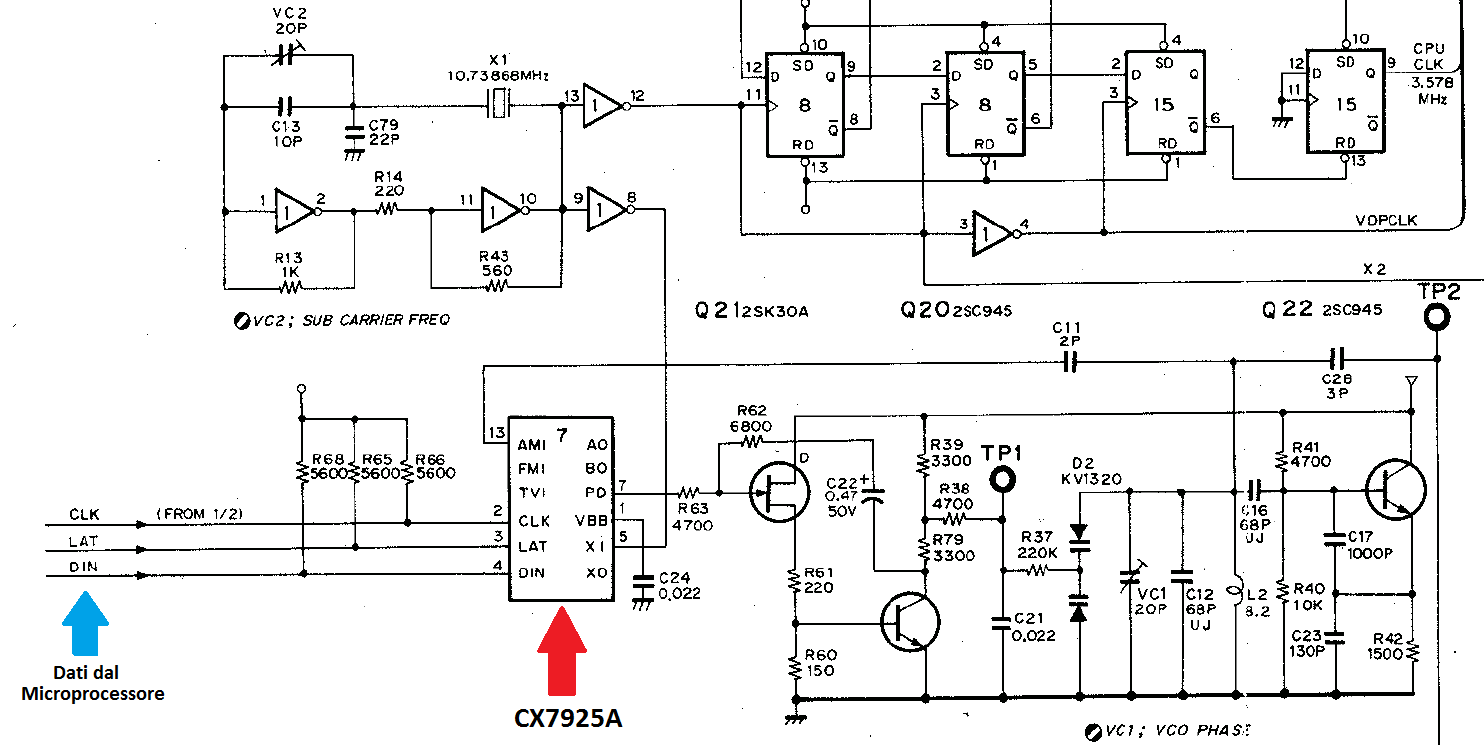

I progettisti dell’MSX in questione si sono trovati perciò con la necessità di ottenere una portante a 4.433618 MHz ma, non avendola a disposizione sulla scheda, hanno deciso di ricavarla dal quarzo da 10.734 MHz già usato per il processore video TMS9929A e per ricavare il clock del microprocessore. Se però ricavare la frequenza necessaria alla CPU era relativamente semplice (bastava dividere quei 10.734 MHz grossomodo per 3 tramite dei Flip-Flop) ottenere invece la frequenza necessaria alla sotto-portante PAL non era così banale.

Questo problema è stato risolto brillantemente con l’uso di un PLL, ovvero di un circuito retroazionato (di cui il chip CX7925A fa parte) in grado di sintetizzare una nuova frequenza partendo da una frequenza base (il suddetto quarzo) tramite una formula matematica (nel nostro caso il CX7925A era in grado di ricevere i parametri di tale formula digitalmente dal microprocessore).

Sfortunatamente trovare documentazione su questo chip è abbastanza difficile e, almeno a me, non è riuscito di trovare altro che uno schema molto semplificato del suo funzionamento interno che tralascia non solo i dettagli, ma anche le informazioni fondamentali per capirci qualcosa. Trovare datasheet descrittivi che ne spieghino il comportamento, i dati che si aspetta in input, le formule da usare, ecc pare essere un’impresa molto vicina all’impossibile anche perché questo particolare chip non è più in produzione probabilmente da qualche decennio.

Il primo passo era dunque quello di capire che dati arrivassero al CX7925A. Di questo si occupa il Firmware dell’MSX all’avvio, ovviamente prima che sia visualizzata una qualsiasi immagine a schermo, ma capire dal codice disassemblato del Firmware che diamine venisse inviato si è dimostrata essere un’impresa tutt’altro che banale. Io il Z80 lo masticavo bene negli anni ’90, oggi me lo ricordo a malapena. Tuttavia, guardando la configurazione delle porte logiche dello schema, mi è parso di capire che l’indirizzo per raggiungere il PLL spaziasse da 3F80h a 3FFFh (ovvero in binario 001111111XXXXXXX dove “X” sta per “non importa”). (Nel firmware disassemblato pare usi quest’ultimo indirizzo, 3FFFh, per riferirsi al PLL)

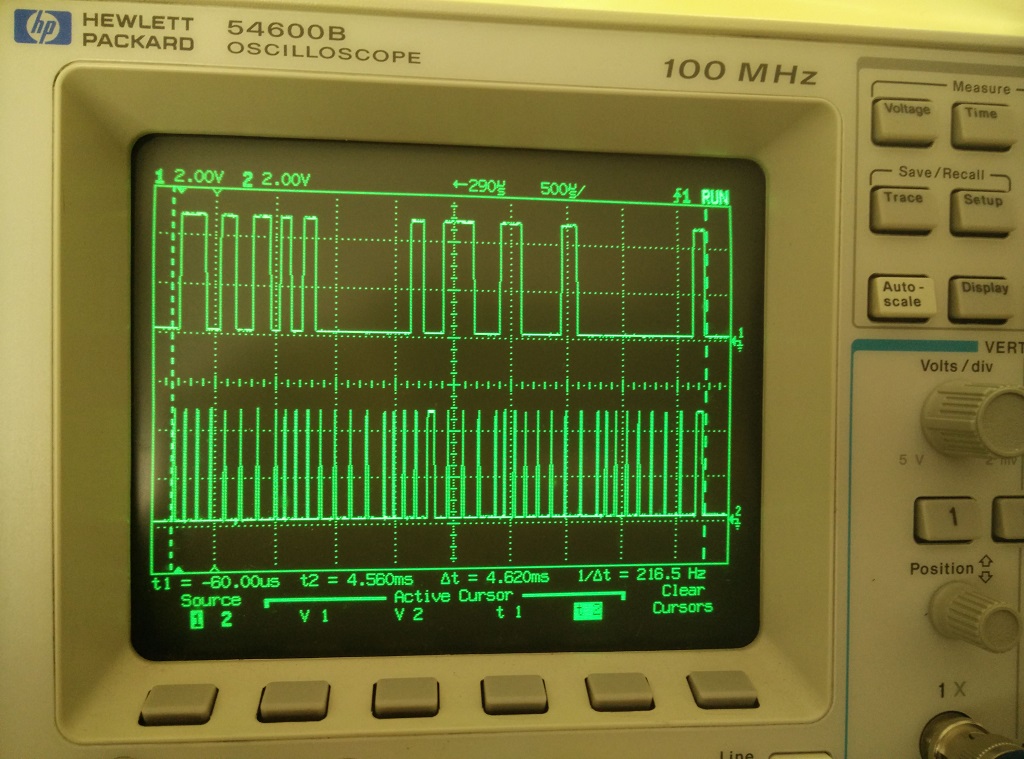

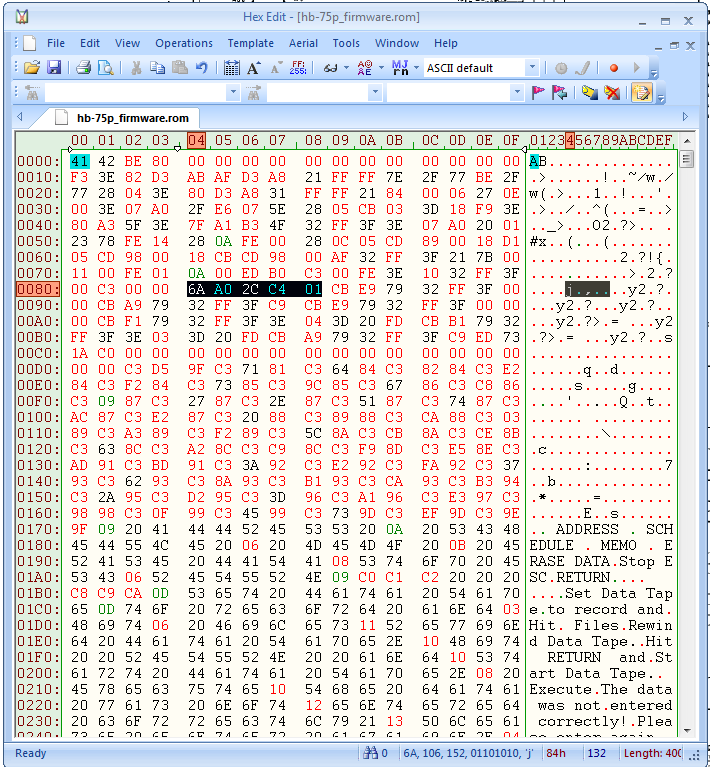

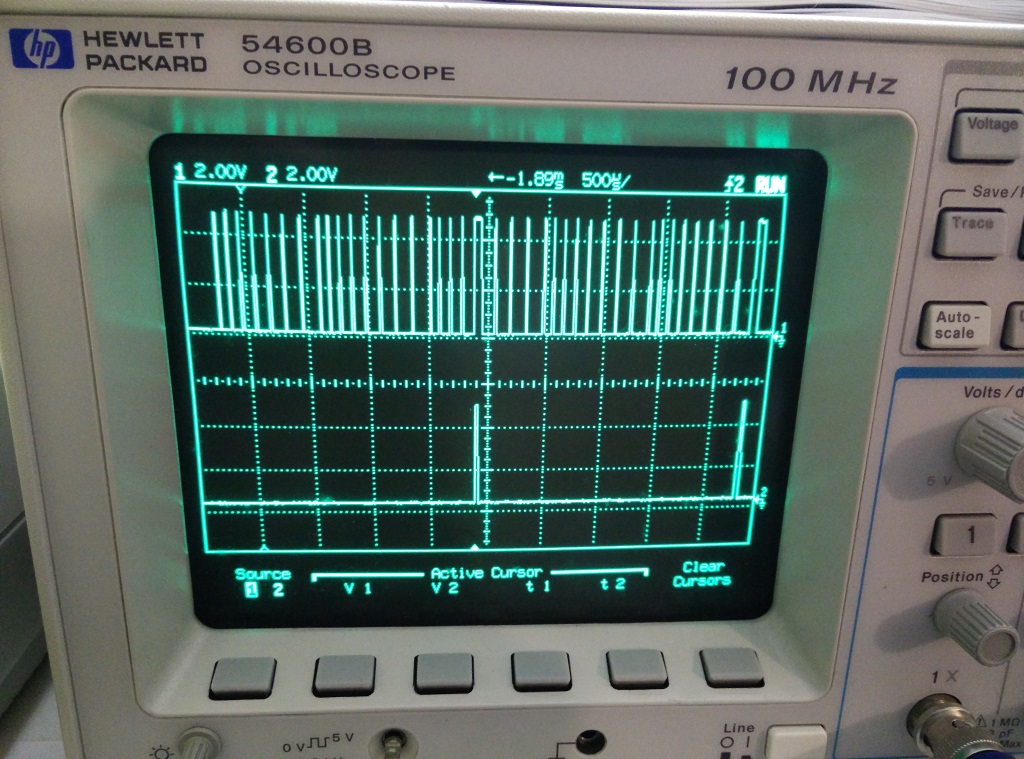

Posizionando il primo canale dell’oscilloscopio su piedino 4 (Data In) e il secondo canale sul piedino 2 (Clock) del CX7925A e dopo un po’ di armeggiamenti con le impostazioni dello strumento, sono riuscito a catturare il burst di dati (della durata totale inferiore ai 5 millisecondi) che il microprocessore invia al PLL al boot. Ad ogni colpo di clock (piedino CLK) il dato binario che si trova sul piedino DIN (Data In) del PLL “entra” nel suo shift register interno (generalmente sui fronti di salita dell’impulso di clock). Il bit che entra per primo sta all’estrema sinistra dell’immagine postata qui accanto mentre ovviamente l’ultimo sta all’estrema destra. Contando i colpi di clock possiamo dedurne subito che il numero di bit entranti è pari a 40.Una volta ottenuto “il fermo immagine” dei dati (dato che non si ripetono nel tempo), utilizzando i cursori dell’oscilloscopio per posizionarmi sui fronti di salita di ogni singolo colpo di clock sono riuscito ad estrarre i 40 bit inviati al PLL, ovvero 0110101010100000001011001100010000000001 o, in esadecimale, 6A-A0-2C-C4-01. Trovati i dati è stato semplice, a quel punto, identificarli all’interno della ROM del Firmware dell’MSX… più semplice di quanto mi augurassi.

Nell’immagine qui accanto è possibile vedere, evidenziati, i byte inviati al PLL proprio all’inizio della ROM del Firmware (indirizzo 0084h) che contiene, fra le altre cose, anche il Personal Data Bank (quel programmino che parte all’avvio e che permette di memorizzare indirizzi, appuntamenti, note, ecc prima di avviare l’MSX-BASIC), bisogna però tenere conto del fatto che la ROM del Firmware ha un indirizzo iniziale di 8000h quindi in realtà questa sequenza di byte incomincerà, in memoria, all’indirizzo 8084h (dello Slot 0).Ora abbiamo i dati che vengono inviati al chip e la loro posizione nella ROM. Tuttavia c’è ancora un dato che non abbiamo considerato e che, sullo schema, è indicato con il nome di LAT (Latch, piedino 2 del CX7925A).

Sfortunatamente, non avendo un’oscilloscopio in grado di visualizzare più di 2 canali per volta, mi è toccato scollegare uno dei due canali precedenti (ho scelto di scollegare Data In). Ho quindi provveduto a spostare il segnale di Clock sul primo canale e posizionare quindi il secondo canale su questo nuovo segnale. Perché ho tenuto il Clock anziché Data In? Perché sono gli impulsi sul segnale di Clock che identificano i singoli bit. Quello che volevo capire era dunque come si comportasse questo nuovo segnale in base ai bit che venivano trasferiti.Dall’immagine qui accanto è possibile vedere che ci sono solo due impulsi sul segnale indicato come “LAT” sullo schema. Uno al 20esimo bit, e il secondo al 40esimo bit. Possiamo quindi dedurne che i dati si suddividono in due gruppi da 20 bit ciascuno. Cosa servano questi due gruppi, senza un datasheet che ne spieghi il principio di funzionamento, è difficile da capire. Evidentemente si tratta di due comandi, uno che forse imposta il divisore, e l’altro, presumo, il moltiplicatore con magari dei bit di configurazione che dio solo sa cosa sono.

Stavo quasi per rinunciare, ma per fortuna, dopo aver ribaltato Internet alla ricerca di qualche goccia di informazione che potesse anche solo mettermi sulla giusta traccia, ho scoperto che la Sony ha prodotto un chip molto simile al CX7925A ovvero il CXD1225M. La buona notizia è che non solo questo chip ha gli stessi segnali di input del nostro PLL, ma qualche buon’anima ne ha digitalizzato il relativo datasheet (che potete visionare cliccando sul link qui sopra).

Ora… la documentazione trovata non necessariamente si applica tale e quale (o per niente) al nostro PLL, però, anche se i due PLL non fossero “intercambiabili” fra loro, potrebbe comunque darci degli indizi sul funzionamento del chip a cui siamo interessati. Leggendo il datasheet fra l’altro si scopre che non solo i segnali di ingresso e uscita del CXD1225M sono praticamente identici al CX7925A, ma anche il CXD1225M si aspetta in ingresso 40 bit, suddivisi in 2 blocchi da 20 bit ciascuno. Riassumendo, abbiamo quindi due PLL, entrambi prodotti dalla Sony, entrambi con i medesimi segnali di ingresso e uscita, ed entrambi con lo stesso numero di bit in ingresso raggruppati allo stesso modo tramite il segnale “LAT” (latch).

Non ci resta a questo punto che provare ad inserire (virtualmente parlando) i dati che abbiamo ricavato nei registri interni del CXD1225M e vedere che succede.

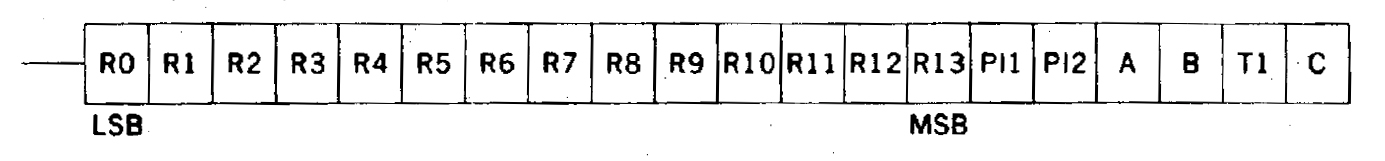

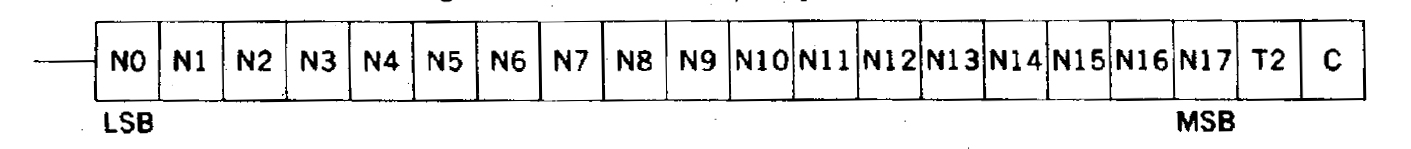

La spiegazione a pagina 5 della scansione chiarisce che per funzionare il CXD1225M necessita di 40 bit in totale di informazione inserita serialmente tramite i tre segnali a noi noti (DIN, CLK e LAT) 20 bit alla volta.

Quando sul segnale “LAT” c’è un colpo di clock i bit inseriti tramite DIN e CLK vengono “analizzati” dal chip e in base al valore binario dell’ultimo bit del gruppo da 20 (chiamato “Bit C” nel datasheet) entrano in uno di due registri.

Questi due registri hanno compiti diversi. Il registro in cui entrano i 20 bit con “Bit C” pari a 0 (nel nostro caso il primo gruppo) controlla il “Reference divider” (ovvero il divisore della frequenza di riferimento da circa 10.734 MHz che forniamo al chip dal nostro quarzo).

Il rimanente registro in cui entrano i 20 bit con “Bit C” pari a 1 (nel nostro caso il secondo gruppo) controlla il “Programmable divider” (che immagino, nel nostro caso, vada moltiplicato alla nostra frequenza di riferimento).

Ora che sappiamo a grandi linee come il CXD1225M funziona proviamo ad inserire i dati a nostra disposizione nei due registri e vediamo che succede.

Il primo gruppo da 20 bit che abbiamo rilevato è questo 01101010101000000010. Come possiamo vedere l’ultimo bit (quello più a destra) è pari a zero, quindi questo gruppo entrerà nel registro che controlla il reference divider. I primi 14 bit sono il nostro divisore (con l’LSB a sinistra), quindi corrisponde al valore decimale 1366 a cui però il datasheet ci dice che dobbiamo sommare 2 quindi abbiamo un divisore della frequenza di input di 1368. I rimanenti 6 bit sono 000010. I 2 bit più a destra (00) sono PI1 e PI2 che, nel nostro caso indicano che stiamo usando il feedback proveniente dal piedino indicato con le lettere AMI. Cosa che corrisponde a quello che osserviamo dallo schema. I successivi tre bit (001) sono A, B e T1 che controllano l’output dai piedini A0 e B0 dell’integrato che, nel nostro caso, sono irrilevanti poiché non collegati. L’ultimo bit (0) è il famoso bit C che abbiamo già usato.

Il secondo gruppo da 20 bit che abbiamo rilevato è invece questo 11001100010000000001. Qui l’ultimo bit (sempre quello più a destra) è pari ad uno, quindi questo gruppo entrerà nel registro che controlla il programmable divider. In questo caso, i primi 18 bit sono (suppongo) il nostro moltiplicatore (sempre con l’LSB a sinistra), che quindi corrisponde al numero decimale 563 a cui, come prima, dobbiamo sommare 2 (perché, come spiega il datasheet, PI1 e PI2 visti prima sono entrambe a zero, ovvero la nostra frequenza di feedback entra dal piedino AMI) risultando in 565. I rimanenti due bit (01) rappresentano rispettivamente T2 (che, da quanto ho capito, viene messo a 1 solo in caso di test del chip e perciò nel nostro caso è a 0) e l’oramai famoso bit C che ovviamente è a 1 per indicarci che siamo nel “programmable divider”.

La formula che ne otteniamo è perciò Fout = Fin * 565 / 1368.

Sapendo che la frequenza di input (Fin) è pari a 10.734 MHz ne otteniamo una frequenza di output (Fout) pari a 4,433267 MHz che è dannatamente vicina alla frequenza che cercavamo. Eventuali piccoli aggiustamenti possono infatti essere effettuati variando la frequenza di input tramite il condensatore variabile indicato nello schema con la sigla VC2.

Nonostante abbiamo fatto molte supposizioni sul funzionamento di questo chip, siamo giunti ad una frequenza praticamente identica a quella che ci serviva. Questo sembra dirci che le nostre ipotesi siano corrette e che, effettivamente, il CXD1225M, da un punto di vista logico, sia molto simile al nostro misterioso CX7925A.

Niente male per essere partiti senza saperne quasi nulla. Naturalmente, se ci sono errori, potete segnalarmeli nei commenti.